工程师们不努力的话,芯片的功耗早就赶上太阳

1967年11月9日,土星5号运载火箭(Saturn V)成功进行首飞,它是人类历史上使用过的自重最大的运载火箭,总推力达3408吨,可以将1艘标准排水量的051型导弹驱逐舰送入太空。

实际上,衡量土星5号有多生猛,除了推力这个指标外,还可以看发动机喷口的功耗密度。一般来说,火箭发动机喷口的功耗密度接近每平方厘米1000瓦。至于万人敬仰的太阳,其表面的功耗密度超过了1000瓦/平方厘米。

在人类科技世界中,还有一样小小的东西,在功耗密度上可以和上面的庞然大物掰掰手腕,它就是芯片。

英特尔第一款商用CPU 4004,是古董级产品,晶体管数量只有2250个,2000年出品的奔腾4处理器,工作频率增加到2.8万倍,晶体管数量增加到2.4万倍。如果晶体管大小不变,工作电压不变,4004版的奔腾4处理器的功耗将增加到天文数字般的6.72亿倍,功耗密度超过瓦/平方厘米,是太阳表面的近20倍。

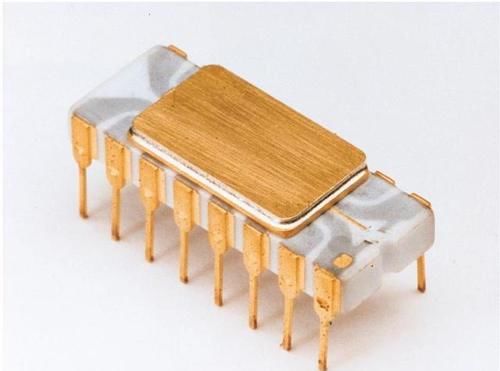

intel 4004

这是理论测算的结果,现实中不可能发生,但芯片的功耗密度之大,上升之快绝非危言耸听,而是迫切的现实问题。

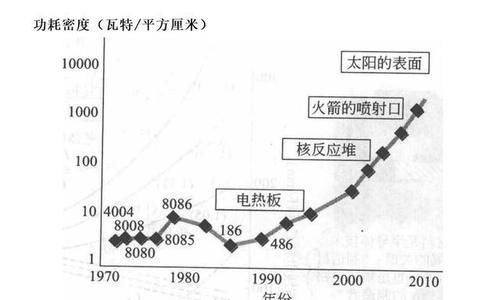

在2001年的国际固态电子电路会议上,专家们指出,处理器的功耗正以指数级的速度增长,如果这个趋势得不到遏制,到2005年时高速微处理器的功耗密度将赶上核反应堆,2010年与火箭发动机喷口不相上下,到2015年甚至可以与太阳表面的功耗密度并驾齐驱。

看起来核物理学家多年求而不得的人造太阳,有可能在芯片大厂手里实现了,这样想的话显然有违科学家的初衷,因为科学们其实是想向芯片行业提个醒,再不想办法解决芯片的功耗问题,南墙在等着你们的脑袋撞上来!

这堵“南墙”在芯片设计领域有个专有名称叫“功耗墙(Power Wall)”,是每一家芯片设计公司和芯片制造厂的必修课:要设计出高性能的芯片,就必须先解决飙涨的功耗问题。

现有的芯片大都是由CMOS(互补金属氧化物)逻辑电路构成,其功耗可以用一个公式粗略表达:

P∝CNV2f

公式中,C为负载电容,N为CPU中的晶体管数量,V为电源电压,f为工作频率。

不要被公式吓到,它概括后就是一句话:降低晶体管尺寸(负载电容减小)、减少晶体管数量、降低电压和工作频率,只要满足其中任何一项,CPU的功耗就会降低。

由于晶体管数量直接关系到CPU的性能和功能(苹果A12 X和A12芯片,麒麟990 5G和麒麟990E的内部架构完全相同,性能差距主要体现在晶体管数量多少),摩尔定律说白了就是堆晶体管的数量,因此每一代芯片的晶体管数量只增不减,这也意味着降功耗就别打晶体管数量的主意了(产品档次区分除外)。

芯片工作频率也和性能相关,DIY时代,电脑超频发烧友最喜欢压榨CPU潜能,压榨的其实就是工作频率,所以也很少有芯片设计商和它过不去。

现在掰着手指头都能算清,工程师们要降低芯片的功耗,有两条路可走。第一条路是减小晶体管尺寸,这是ASML和台积电们的职责,制造分辨率更高的光刻机,把工艺制程从微米级一点点演进到纳米级,就是为了把晶体管做得小一点,降低负载电容,从而降低功耗。

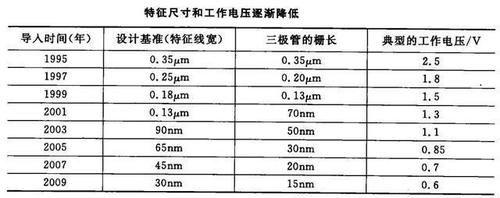

通过海量烧钱,工程师已经把晶体管的尺寸做得极其微小,目前量产的A14芯片和麒麟9000芯片,晶体管的栅长为5nm,仅为已知最小的动物病毒猪圆环病毒直径的1/3左右,而在1995年,晶体管的栅长还只能做到350nm。也就是说,今天的芯片仅仅因为尺寸缩小,导致功耗仅有25年前的1/20左右。

第二条路是让芯片这匹“马儿”吃得少一点,即降低芯片的电源电压。这条路由于没有昂贵的光刻机和海量烧钱的生产线做广告博取眼球,很少有人知道。

降低电压有个最大的好处就是主要烧智力,而且相比做小晶体管尺寸的节能效果,更为生猛。根据上面的公式可以知道,电源电压和芯片能耗呈平方关系,也就是说电压每降低到原来的1/2,能量消耗就减少到原来的1/4,这种指数级的关系,搞好了是相当惊人的。

2011年9月16日,芯片大户英特尔公布了一款邮票大小的CPU,开发代号Claremont,它的特别之处就是“吃”的特别少,低负载时耗电量仅为10毫瓦,要知道现在手机SoC芯片中一颗CPU大核满载时,功耗就有1瓦,是Claremont的100倍。英特尔没有说明Claremont的电压是多少,但应该比手机CPU内核低得多,估计在1/10左右。

上一篇:阁巷高新产业小微园:园区来了专业服务“多面

下一篇:没有了